레지스터에 저장된 데이터들이 각각의 전송 라인을 사용한다면 선이 너~무 많아지기 때문에

버스라는 공통 라인을 사용한다.

버스에서는 한 번에 하나의 전송만 이루어지도록 제어신호를 이용하여 전송에 사용될 레지스터를 선택한다.

비유를 하자면 학교에 가기위해 학생 한명한명이 전부 자가용을 끌고간다면 학교에 자동차가 포화될것이다.

따라서 학교 통학버스를 이용하는데 한번에 모든 학생이 탑승할 수 없으므로 한명씩 누구탈래? 물어보는 제어를 통해서 탈 사람을 고르게 된다. 내릴 때도 마찬가지이다.

대표적으로 버스를 설계하는 방법 2가지를 설명하겠다.

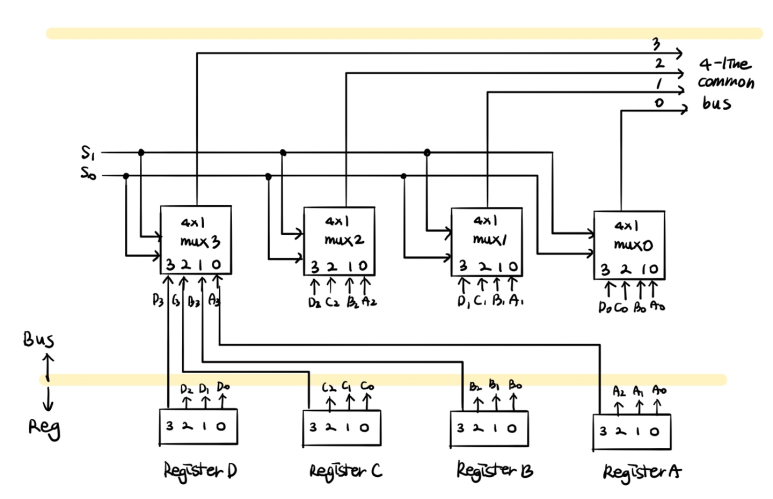

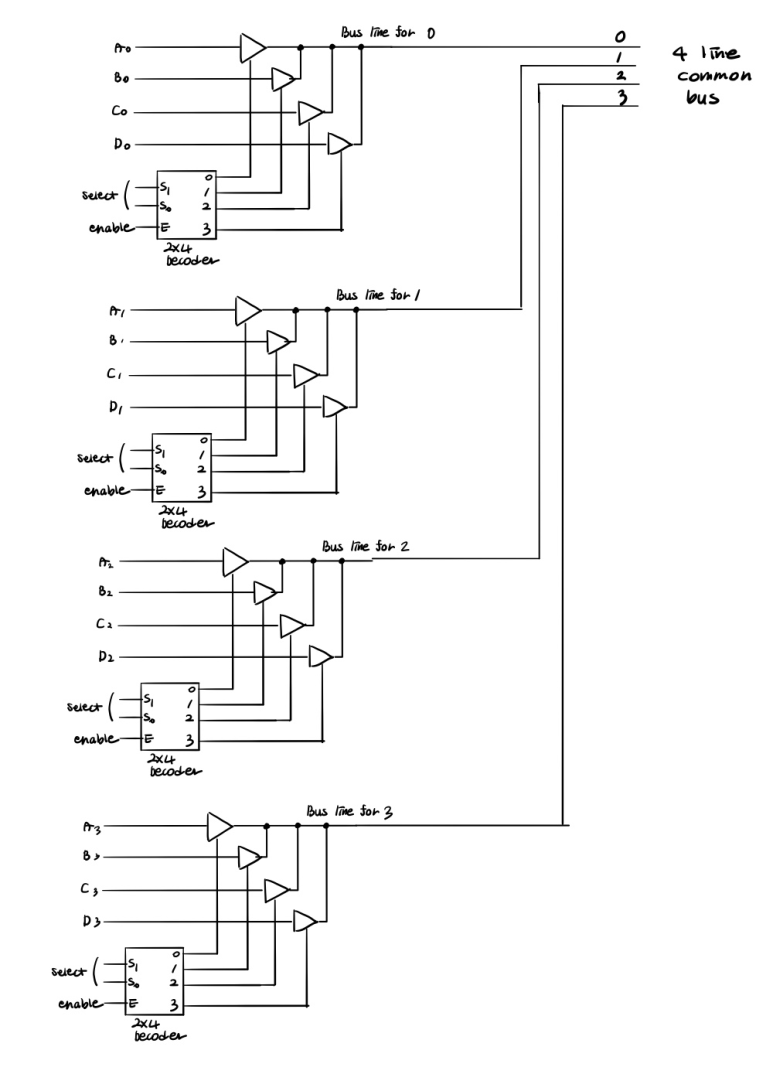

1) 네 개의 레지스터를 이용한 버스 시스템

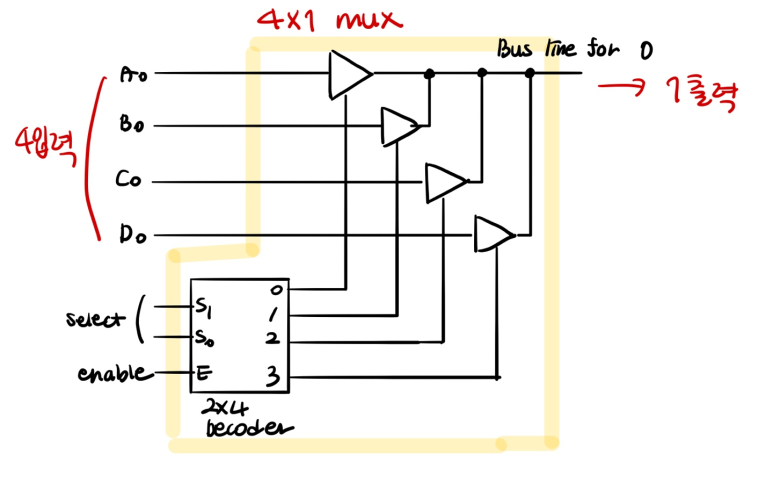

노란색 선을 기준으로 버스 부분과 레지스터 부분을 나누어 볼 수 있다.

레지스터는 A,B,C,D 4종류가 존재하고, 데이터 비트수는 4비트다.

모든 레지스터는 자신의 비트들을 버스에 올릴 것이고, 그 중 어떤 레지스터를 선택할지 고르는 것은 멀티플렉서가 수행하게 된다.

4x1 멀티플렉서는 A,B,C,D 레지스터중 하나를 select 신호에 의해 하나 선택하게 되고, 선택한 비트를 출력으로 내놓은는다. 각각의 MUX들은 레지스터의 0~3번비트를 입력단으로 받고 출력한다.

말로만 하면 이해가 잘 안될테니 그림으로 설명하겠다.

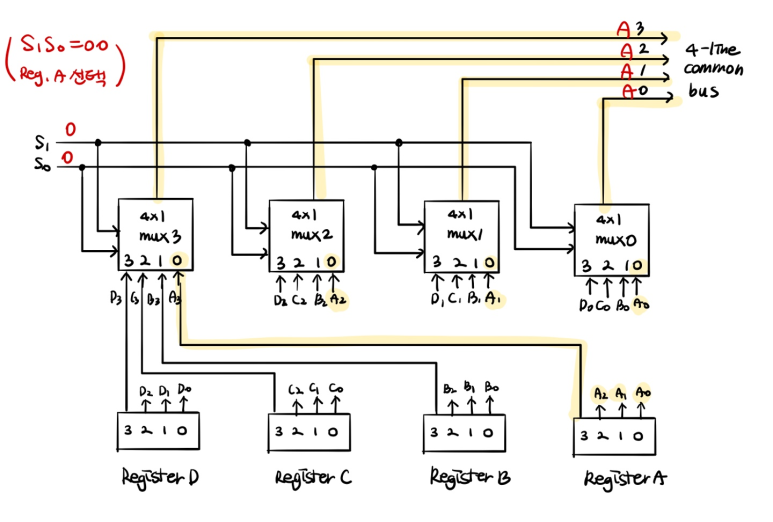

아래는 레지스터 A가 선택되는 그림이다.

select 신호를 A를 선택할 수 있도록 00을 보내주면 각각의 mux들은 A를 선택하여 출력단으로 내놓게 된다.

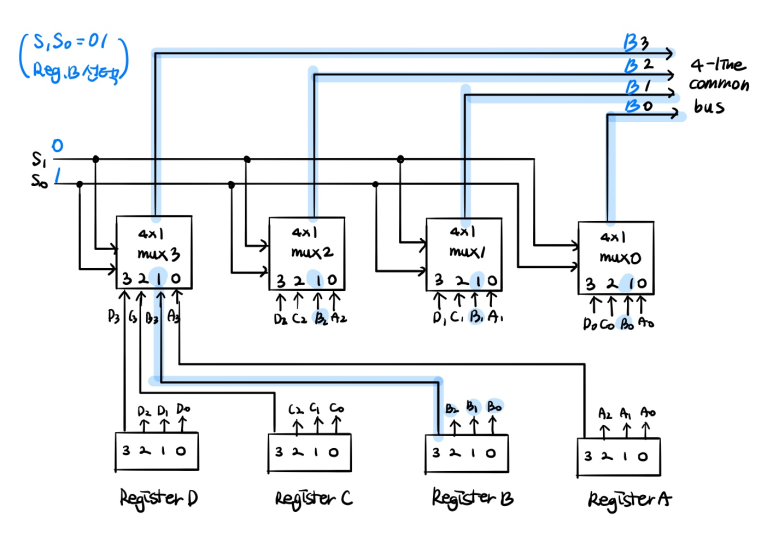

레지스터 B를 선택하는 과정도 아래와 같다.

레지스터 B를 선택하기 위해서는 select신호를 01을 넣어주었다.

레지스터 C와 D도 이와 마찬가지 과정을 거친다.

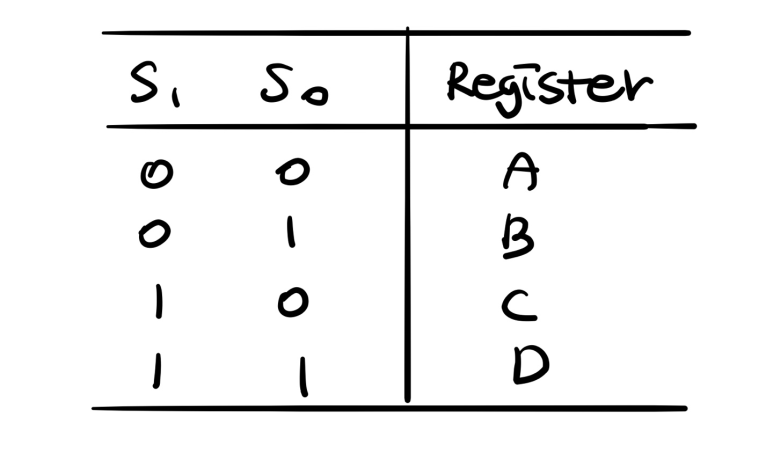

레지스터를 선택하는 select신호를 표로 정리하면 다음과 같다.

네 개의 레지스터에 대한 버스시스템의 select신호 표

2) 3-상태 버스 버퍼를 이용한 버스 시스템

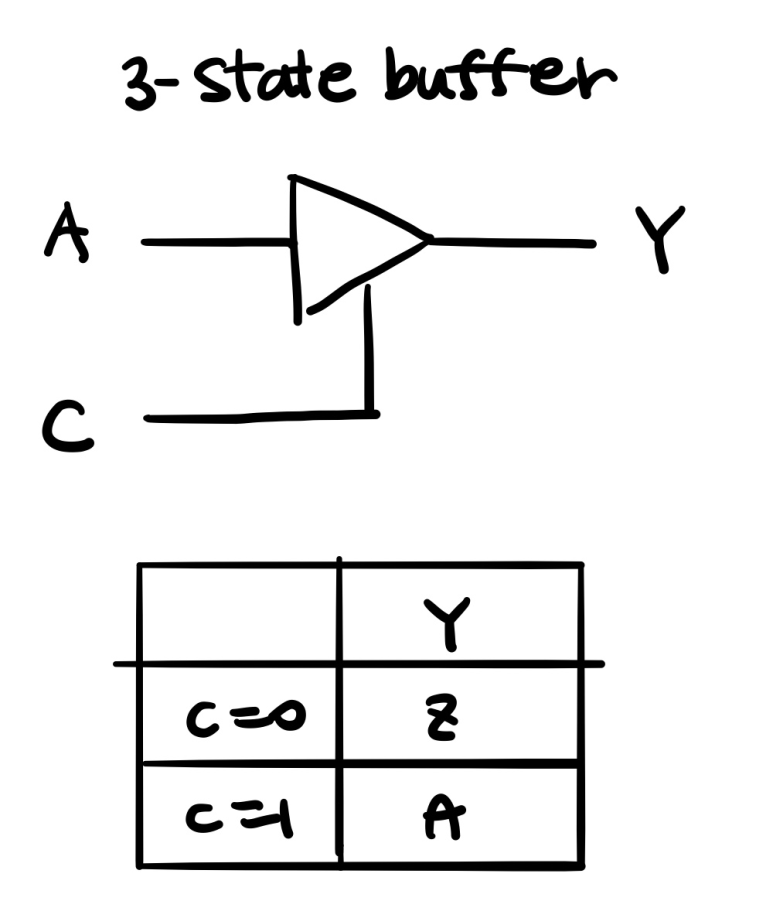

3-상태 버퍼는 control 입력의 값에 따라서 출력하는 값이 (0,1) 이거나 고저항 상태(z)이다.

따라서 3 상태 버퍼는 출력 값이 0,1,z 로 3가지가 존재한다.

위 그림과 같이 3 상태 버퍼는 2가지 입력 A, C를 가진다.

A는 보통 입력 값이고, C는 제어 입력이다.

만약 C=1 이라면 출력 Y는 입력 A를 내보낸다.

C=0이라면 출력 Y는 입력A가 아닌 고저항 상태 Z를 가지게 된다.

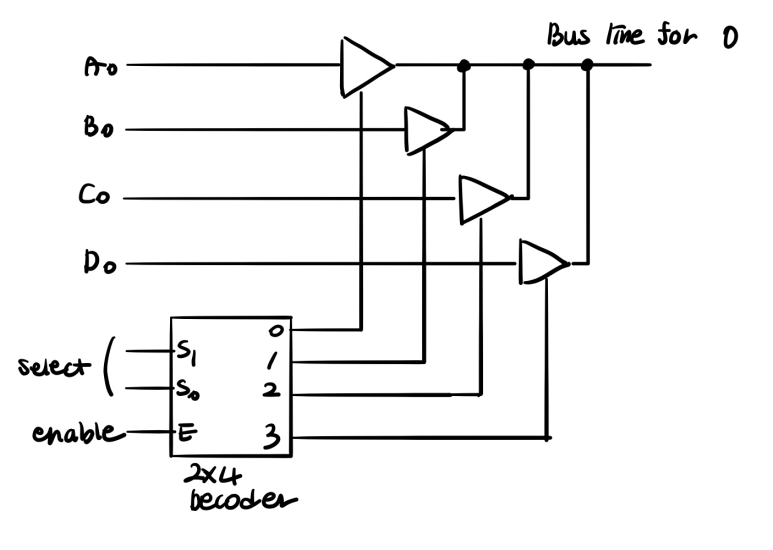

이를 이용한 버스시스템은 다음과 같다.

(그림 1) 3 상태 버퍼 버스 시스템

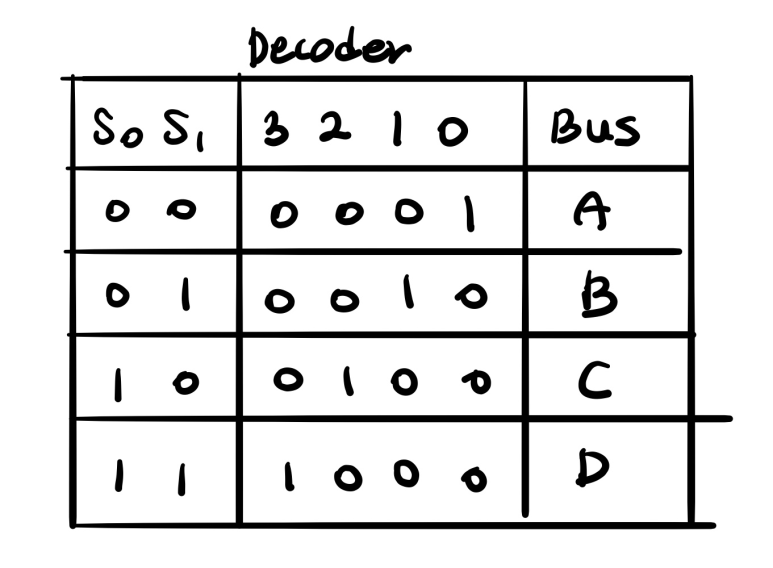

(표 1)3상태버퍼 버스의 출력 표

그림 1은 3상태 버퍼 시스템을 나타낸다.

select 신호는 디코더에 의해서 4개의 출력으로 나타나게 된다. 각각의 출력들은 3상태 버퍼로 들어간다.

만약 3상태 버퍼에 들어온 값이 1이라면 보통 입력단에 들어온 값을 내보낼 것이고

들어온 값이 0이라면 고저항상태 Z가 될것이다.

이 고저항 상태의 특성 덕분에 로딩 효과(loading effect)에 대한 염려 없이 하나의 라인에 여러 개의 3-상태 게이트 출력을 연결하여 공통 버스 라인을 구성할 수 있다.

즉 고 저항 상태에 의해서 라인이 끊어진 것과 같은 상태가 되고, 버스엔 하나의 입력만 들어오는 상태가 되기 때문이다.

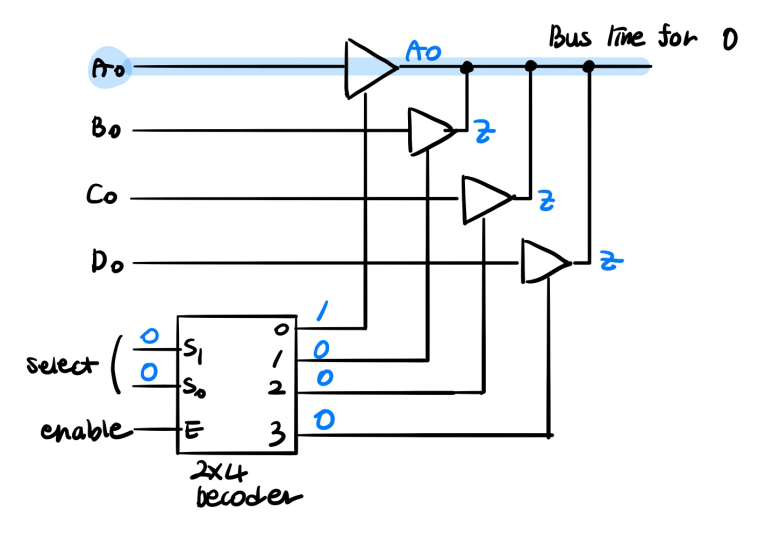

이제 레지스터를 선택하는 과정을 자세히 살펴보자.

레지스터 A의 입력을 선택하는 과정을 아래와 같은 그림으로 설명할 수 있다.

select 신호는 레지스터 A를 선택하기위해 00이다.

디코더에 의해 출력단자 0만 1이고 나머지는 0이다. 따라서 3상태 버퍼에서 A라인 빼고는 전부 Z 상태를 가지게 되어서 버스에는 A값만 올라가게 된다.

하지만 위와 같은 그림은 1비트만 표현한 것이다.

4비트 레지스터를 선택하는 것은 아래와 같은 그림과 같은 구조를 가지게 된다.

참고로 여기서 3상태 버퍼는 4비트 4x1 멀티플렉서와 같은 동작을 수행하게 된다.

따라서 4x1 멀티플렉서를 위와 같이 설계할 수 도 있겠다.

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 산술 논리 시프트 장치 (ALU) (0) | 2021.06.25 |

|---|---|

| [컴퓨터 구조] 논리 마이크로연산, 시프트 마이크로 연산 (0) | 2021.06.25 |

| [컴퓨터 구조] 산술 마이크로 연산 (0) | 2021.06.25 |

| [컴퓨터 구조] 레지스터 전송 (0) | 2021.06.25 |

| [컴퓨터구조] 부동소수점(10진수 2진수) (0) | 2021.06.25 |