마이크로 연산이란 레지스터에 저장된 데이터에 대해 수행되는 기본적인 연산이다.

크게는 네가지로 나눌 수 있다.

1) 레지스터 전송 마이크로 연산

2) 산술 마이크로 연산

3) 논리 마이크로 연산

4) 시프트 마이크로 연산

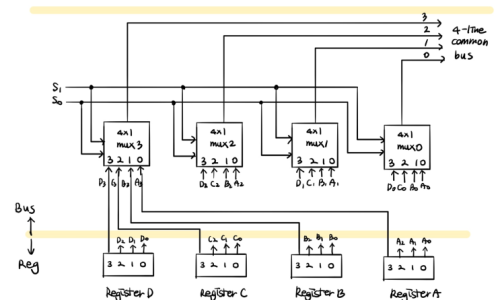

1) 레지스터 전송 마이크로 연산

여기서 레지스터 전송 마이크로 연산은 이전 블로그 포스팅에서 확인할 수 있다.

https://programming-hee.tistory.com/3

[컴퓨터구조] 버스와 메모리전송 (multiplexer, 3 state buffer)

2) 산술 마이크로 연산

산술 마이크로 연산이란 레지스터 안에 들어있는 값들을 더하거나 빼는 과정을 뜻한다.

레지스터 A에 들어있는 값과 레지스터 B에 들어있는 값을 가지고 산술 연산을 하는 것을 예시로 들겠다.

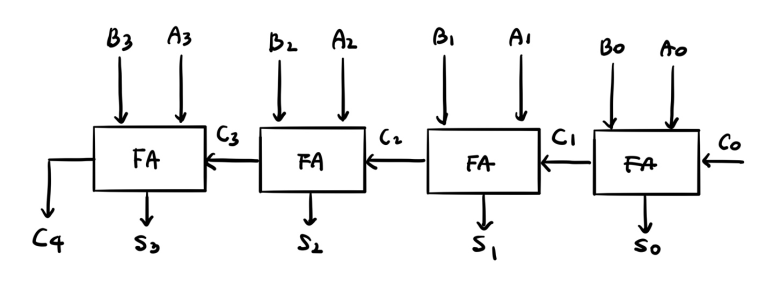

대표적인 덧셈을 하는 연산기는 아래와 같은 이진 가산기가 있다.

4비트 2진 가산기

다들 전가산기(full adder)는 알고 있겠지만, 전가산기는 2개의 1비트 데이터의 덧셈을 수행하는 가산기다. 그것을 4개 이어 붙이면 위와 같은 4비트 2진 가산기가 된다.

(전가산기가 모른다면 공부를 하고 와야함!)

덧셈은 위와 같이 하면 되겠는데, 그렇다면 뺄셈은 어떻게 설계할 수 있을까?

컴퓨터에서 뺄셈은 2의 보수를 더하는 과정으로 대체될 수 있다.

즉 A - B 는

A + (B의 2의 보수) 이다.

2의 보수를 구하는 과정은 이미 알고있겠지만, 간단히 설명하자면

1의 보수를 취한 다음 1을 더해주면 된다.

예를 들자면 0101 을 1의 보수 취하면 1010 이 되고, 거기에 1을 더하면 1011이 된다.

따라서 0101의 2의 보수는 1011이다.

그렇다면 B의 2의 보수를 논리적으로 표현하자면

B의 보수 + 1 즉, B'+1이 된다.

따라서 A-B는 A+B'+1로 나타낼 수 있겠다.

가산기와 감산기가 따로 존재한다면 회로의 크기가 커지므로, 합쳐버리는게 편할것이다.

어차피 감산기 또한 가산기와 동일하게 덧셈을 수행하기 때문이다.

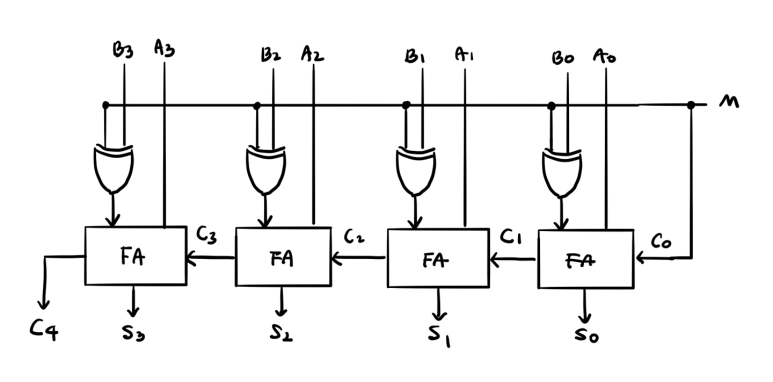

따라서 가감산기는 다음과 같이 설계할 수 있다.

4비트 가감산기

처음에 소개했던 가산기와 거의 유사하지만 XOR 게이트가 추가된것을 확인할 수 있다.

이 XOR 연산기가 감산기와 가산기를 선택하여 수행할 수 있게 한다.

만약 M=0 이라면 XOR 연산 결과 ( B xor 0 = B ) 가 되어, FA에 B 그대로 들어갈 수 있게 된다.

즉 A+B 연산을 수행하게 되어 가산기와 동일한 연산을 수행한다.

만약 M=1 이라면 XOR 연산 결과 ( B xor 1 = B' ) 가 되어, FA에 B의 1의 보수가 들어가게 된다. 이때 캐리 C0 또한 M의 값 즉 C0=1이 되어 FA에 캐리로 들어가게 되어 A+B'+1 연산 즉 A-B 을 수행하게 된다. 이는 감산기와 동일한 연산이다.

정리한다면 다음과 같다.

M=0 : A+B (가산기)

M=1 : A+B'+1 = A-B (감산기)

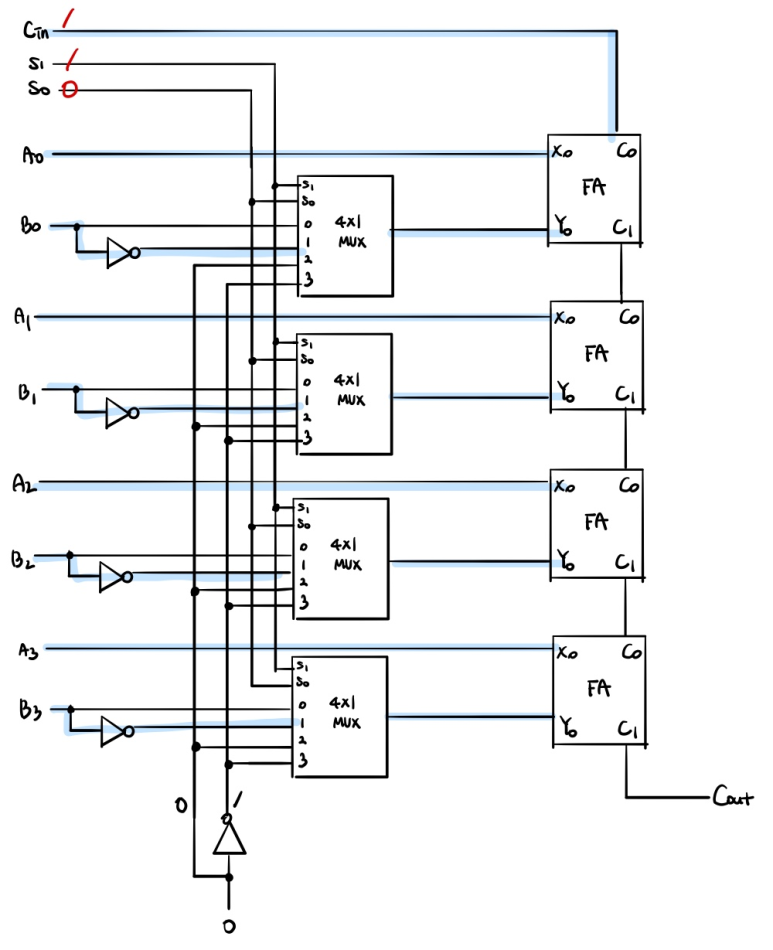

최종적으로 4비트의 산술 연산을 수행하는 회로를 설계할 수 있다.

이 회로는 덧셈 뺄셈과,1씩 증가하거나 1씩 감소하는 연산도 포함하는 온갖 덧셈 뺄셈 연산은 집어 넣은 회로이다.

4비트 산술회로

위와 같은 산술 회로는 다음과 같은 함수표로 정리될 수 있다.

산술 회로의 함수표

어려워 보이지만 겁먹을 필요가 없다.

하나하나 천천히 입력값을 회로도의 선을 따라가며 넣어보면 된다.

잘 보면 FA가 4개 존재한다. 이것은 초반에 언급했던 이진 가감산기와 동일하다.

가감산기에서는 XOR로 B의 입력을 그대로 또는 보수 시켜주었는데, 이 산술 회로에서는 멀티플렉서를 이용하여 B의 값을 선택할 수 있다.

B에는 complement가 달려있는 것을 확인할 수 있는데 그것은 B를 보수화 시켜주어 mux의 2 입력에 들어가게 되고, select신호에 의해 선택되면 FA의 입력으로 들어갈 수 있다.

즉, 뺄셈 연산을 수행하게된다.

말로 설명하는 것 보단 그림으로 보는게 낫다.

아래는 A+B를 수행하는 과정이다.

select 신호가 00 이고, Cin은 굳이 설정해주지 않았다. 0이 들어가든 1이 들어가든 FA에서는 그저 더해질 뿐이다.

중요한거는 B의 입력이 보수화 되지 않고 B 그대로 mux에서 선택되어 FA로 들어가게 된다는 것이다.

그를 통해서 A+B 연산을 수행할 수 있다.

이제 뺄셈 연산을 살펴보자.

이때는 Cin이 중요해진다.

뺄셈 연산을 위해서는 B를 1의 보수화 시켜준 다음, 1을 더해주어야 하는데

그 더해주는 1이 Cin이다.

즉 A+B'+1 = A+B'+Cin 인 것이다.

이런식으로 뺄셈 연산을 수행할 수 있다.

나머지는 A에 1을 더해주거나 A를 그대로 출력하거나 하는 연산인데 함수표를 보면 충분히 이해할 수 있을 것이다.

나머지 논리, 시프트 마이크로 연산은 다음 포스팅에서 자세히 설명하겠다.

'Computer Science > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 산술 논리 시프트 장치 (ALU) (0) | 2021.06.25 |

|---|---|

| [컴퓨터 구조] 논리 마이크로연산, 시프트 마이크로 연산 (0) | 2021.06.25 |

| [컴퓨터구조] 버스와 메모리 전송(multiplexer, 3 state buffer) (0) | 2021.06.25 |

| [컴퓨터 구조] 레지스터 전송 (0) | 2021.06.25 |

| [컴퓨터구조] 부동소수점(10진수 2진수) (0) | 2021.06.25 |